# JOURNAL

#### In This Issue:

- Atmel's ARM-based Flash  $\mu$ Cs Optimized for Real-time Control Applications

- Reconfigurable System on a Programmable Chip Platform

- Practical Aspects of ARM®

Core-based Product

Development

- Designing for Efficient Production with In-System Re-programmable Flash  $\mu\text{Cs}$

- Naval Research Lab's Data Acquisition Module for DSP

- Simplified Ethernet Stack Core, or How to Reduce System Cost

- A Low-end Approach to Tamper-proof Energy Metering with the AVR465

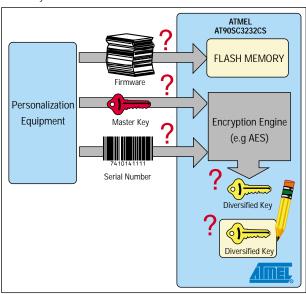

- Limiting Illegal Hardware Copies by Using Secure Hardware Authentication

- Is Security Needed in Your Memory Application?

- Implementing

DES/3DES with Atmel

FPSLIC™

- Wireless MP3 Remote Jukebox with Atmel AT90S2313-4PC

- Song Quality Improvement Using the DAC on AT89C51SND1 Reference Design

- Easy Image Processing: Camera Interfacing for Robotics

- Atmel Raises the Bar on Tire Pressure Monitoring Systems

- Setting the UNIX/Linux Environment to Develop an AVR Application

- Using STK500 Under UNIX/Linux Environment

## Different architectures from Atmel – one solution from IAR Systems

Secure your

investment in application

code development and

re-use your code in any

Atmel device.

IAR Embedded Workbench®

supports the Atmel AT89,

AT91 and AVR families.

#### IAR Embedded Workbench® for any Atmel MCU

The state-of-the-art integrated development environment with a highly optimized IAR C/C++ compiler and versatile IAR C-SPY™ source and assembly level debugger. Full support for the AT89, AVR and AT91 (including SAM7) families.

IAR Embedded Workbench for 8051 v 6.10 brings the most compact code to all AT89 users. With all powerful new features introduced, this is the most efficient C development tool on the market.

#### IAR visualSTATE® for any Atmel MCU

The only state machine design tool for embedded systems generating micro-tight C code.

### Visit us at WWW.iar.com

Download evaluation versions today, and find out for yourself how easily you can develop and re-use your application code across different Atmel platforms.

#### Introduction

By Jeff C. Katz, VP Marketing, Atmel

#### Introduction

Welcome to Atmel's Application Journal, Vol 4.

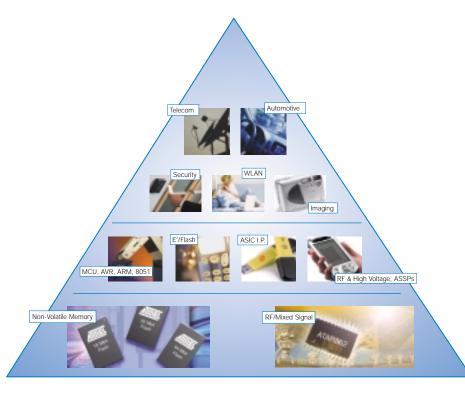

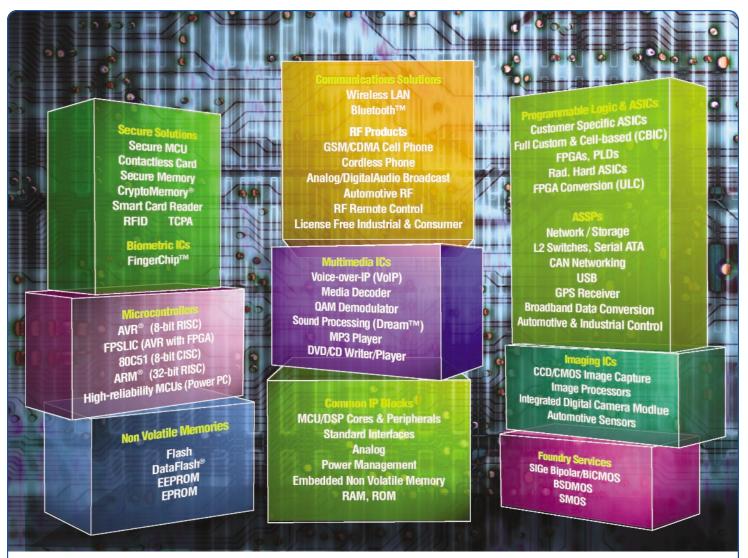

In every issue of the Applications Journal we strive to provide our readers, the electronics design engineering community, with a strong representation of our ability to offer technology for complete systems, including System Building Blocks like our microcontroller lines, Basic Technologies such as non-volatile memory and RF/Mixed Signal, and Complete System Solutions for the leading embedded applications (as exemplified in the illustration below).

Readers of previous issues will notice some subtle changes in the way we are now formatting the Applications Journal: each issue in the future will be segmented into key applications sectors such as Industrial, Consumer & Computing, Wireless, Automotive and Security. Each application section will carry applications articles on creating product designs using Atmel's products and embedded and applications-specific tools and services from our partner's suppliers.

In addition, this issue features articles covering recent initiatives involving Atmel's AVR microcontroller family and some key applications associated to current and future designs taking advantage of the benefits afforded by this IC family. For those looking for more processing power we feature two applications involving our 32-bit ARM support for today's market requirements. We also continue to carry our popular "Designer's Corner" and "Code Patch" sections for our readers who wish to go a little deeper into the content and access the code shortcuts (this time featuring the UNIX/Linux environment) provided in each issue.

We trust that the articles will provide a clear understanding of how you can use Atmel's product line-up to meet your exacting demands within key areas of these application segments—such as GPS design, automotive safety, computer and network security and residential/industrial wireless data transfer. Within these areas of end-product design we feature the complementary nature of our product lines and how to get the most from working with us and getting all the support you need, both from Atmel as well as our worldwide tools and engineering support from independent suppliers.

Throughout 2005 and beyond, Atmel will continue to provide you, our customers, with the standard products, application-specific standard products (ASSPs) or customer-specific products (ASICs) in order to allow for a rapid and flexible response to the needs of your customers.

#### Introduction

**Introduction** Jeff Katz, Atmel

Atmel News News & New Product Releases

#### Microprocessors In-Depth

Reconfigurable System on a 9 **Programmable Chip Platform**

by M. Danek, P. Honzik, J. Kadlec, R. Matousek, and 7. Pohl

**Practical Aspects of ARM Core-based Product Development** by Jim Hallman

#### Designer's Corner

**Designing for Efficient Production** with In-System Re-programmable Flash µCs

by OJ Svendlsi

#### [ndustria] & Military Applications

Naval Research Lab's Data Acquisition 18 Module for DSP

by Flemming Christensen

Simplified Ethernet Stack Core or, **How to Reduce System Cost**

by Guy Lafayette

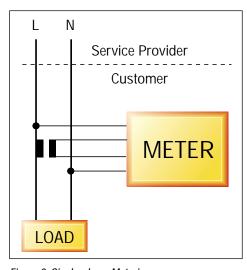

A Low-end Approach to Tamper-proof 2 **Energy Metering with the AVR465**

by Kim Meyer

Is Security Needed in Your Memory **Application?** by Mary T. Jarboe

Implementing DES/3DES with Atmel FPSLIC

bv Axel Sikora

#### **Wireless Applications**

by Brian Miller

**37** Song Quality Improvement Using the DAC on AT89C51SND1 Reference Design

**Easy Image Processing: Camera Interfacing for Robotics** by Daniel Herrington

#### Automotive Applications

44 Atmel Raises the Bar on Tire Pressure **Monitoring Systems** by Markus Levy

Code Patch

46 Setting the UNIX/Linux Environment to **Develop an AVR Application** by Daniel Widyanto

Using STK500 Under UNIX/Linux Environment

by Daniel Widyanto

## **Atmel News:**

More information on the products and services in these articles can be found at www.atmel.com

### Emerson Corporation Strategic Supplier Award

Atmel was one of two semiconductor suppliers recognized for exceptional Quality, Service and Customer Support. Presenting the award is Ahmad Kian, Director of Strategic Sourcing, Rosemont Process Management Division, Emerson Corporation. Atmel's Ray Barth, District Sales Manager, accepts the award on behalf of the Corporation. This is the second consecutive year that Atmel received this prestigious Award.

### WiMAX and Atmel Target Broadband Wireless Market

Atmel has announced its Principal membership in the WiMAX Forum™, an industry-led organization that promotes the interoperability and certification of broadband wireless products based on the IEEE 802.16 standard. As an experienced manufacturer of advanced wireless semiconductors, Atmel will play an important role in the design, production and marketing of silicon to be used in WiMAX Forum Certified™ applications for this key emerging market.

The WiMAX Forum is striving to create economies of scale made possible by standards-based, interoperable products that drive price and performance levels not achievable by proprietary approaches. WiMAX technology is designed to help service providers across global markets deliver economical broadband data, voice and video services to both residential and business customers.

Frank Draper, Director of Membership at the WiMAX Forum, says, "Atmel will be a significant contributor to the WiMAX Forum bringing their vast experience as a wireless IC manufacturer and their unique ability to offer complete out-of-the-box solutions."

### **Media Processor for Digital TVs and Projectors**

Atmel's next generation media processor, the ARM7TDMI™ core-based AT76C120, is ideal for standard and high-definition TVs, flat-panel displays, projectors, portable media servers, and standalone playback boxes. The AT76C120 integrates all the functions required to implement media playback functions onto a single chip. Atmel's Director of Multimedia Products, Tassos Markas, remarked, "With the introduction of the AT76C120 device, Atmel is enabling a new line of consumer products with rich media capabilities. Our goal is to enhance the digital experience and allow consumers to enjoy their media content in their native high

resolution. The AT76C12O device has the processing power and performance to just do that."

The AT76C12O device supports high performance still-image and video decoding of media files encoded according to JPEG, MPEG4, MPEG1, Motion JPEG standards as well as of other popular media formats found in digital still cameras. The device contains a high-speed flash card interface that allows quick access to high-resolution images, video and audio streams stored in flash cards by digital still cameras, video cameras, PDAs or camera phones.

Production samples, evaluation boards, software libraries, as well as full application software are available now. The part is priced at \$8 for quantities of 100,000 parts.

## Atmel Receives 2004 Frost & Sullivan Award for Smart Card IC

Frost & Sullivan announced at the Smart Card Alliance Conference in San Francisco, that Atmel has been presented with the prestigious Frost & Sullivan award for Global Competitive Strategy Leadership, in recognition of its achievements in the smart card IC market throughout 2003. "Atmel's ever-rising market ranking and market shares each year validate its success in the smart card IC industry," said Prianka Chopra, Smart Cards Program Manager at Frost & Sullivan.

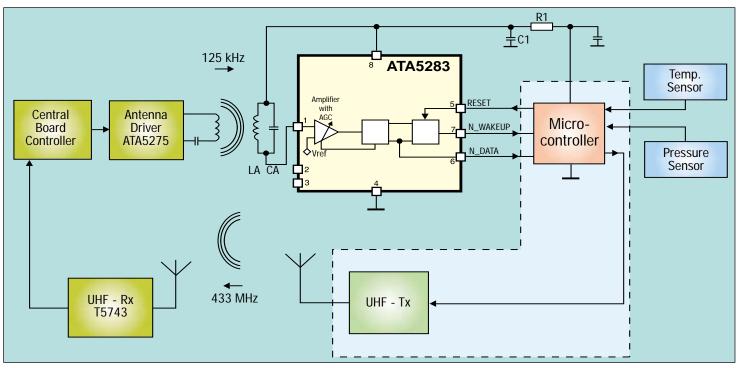

## New Highly LF Antenna-driver IC for Automotive Tire Pressure Monitoring Applications

Atmel announced at the Convergence Show in Detroit last month the release of a new IC for automotive Pressure-on-Demand (POD) systems in Tire-Pressure Monitoring System (TPMS) applications. POD systems provide the automotive industry's highest flexibility during wheel change and for TPMS system operation. Also, they help to reduce RF noise since the driver stage is placed together with the antenna inside of the wheel well. The ATA5275 features the highest integration for embedded automotive systems and maximum performance. Due to its self-tuning resonance capability, the antenna is able to operate with maximum voltage, maximum current and maximum field strength. The ATA5275 extends Atmel's broad TPMS product portfolio, which already includes UHF transmitter and receiver ICs, LF receiver and antenna driver ICs as well as microcontroller devices to design complete TPMS systems.

Comparable solutions are usually designed as discrete solutions, where the system is not integrated, requiring more design effort, more external devices and a higher bill of materials. The new ATA5275 is the first non-discrete antenna driver IC available on the market, making TPMS/POD designs simpler and more cost-effective. The device is highly integrated, and also provides a microcontroller interface (bi-directional K-line interface) that allows the transfer of diagnostic data.

## Trusted Computing Standard Extended to Embedded Systems

Atmel has announced the AT97SC3201S Trusted Platform Module (TPM), a single-chip hardware security subsystem designed specifically for embedded systems, such as voting machines, gaming systems, PDAs, set-top-boxes, POS terminals, ATMs, portable mass storage devices, and industrial controls. Based on Trusted Computing Group industry standards, the new device offers embedded systems ultra-security that, until now, has only been available for personal computers.

According the Kevin Schutz, Atmel's Product Line Manager for Trusted Platform Modules, "The AT97SC3201S gives embedded systems the capability to provide a variety of software integrity measurements, perform mutual authentication processes, and present credentials that have not been available to embedded system designs before. Now any embedded system can take advantage of hardware security based on TCG standards."

Price and Availability - The 3.3 volt AT97SC3201S is available immediately and is priced at \$4.50 in quantities of 10,000.

The new antenna driver IC provides several diagnostic features such as short-circuit, open-circuit and over-temperature detection. The IC is load-dump protected up to 45 V and operates directly from the car battery. The ATA5275's time-out interface supervisor serves to avoid

unintended continuous transmission in case of line errors. The temperature range is -40°C/-104°F to +105°C/221°F. Samples of the antenna driver IC ATA5275 in QFN20 packages are available now. Pricing starts at 1.94 US \$ (10k).

## Two New Physical Layer Chips Target Network Storage, PC and Consumer Electronics Markets

Two new PHY (Physical Layer) stand-alone chips from the Serial ATA (SATA) product family targeted for PC and a range of storage applications such as SATA Host/Device Controllers, Redundant Array of Independent Disks (RAID) and Network Attached Storage (NAS) and SAN Storage Area Networks are now available from Atmel. Other applications include Router Switches that can also be integrated in consumer electronic products such as set-top-boxes. The AT78C5081 is a single port and AT78C5090 is a dual port Serial ATA PHY, that both exceed the parameters necessary to be compliant with the Serial ATA Gen1 revision 1.0 specification therefore providing a very high-speed data transmission at 1.5 Gbps.

"Atmel Network Storage Products BU is dedicated to designing high performance products for PC, networking and consumer products, by making the Serial ATA Physical Layer available as a stand-alone product in the market. We are able to provide more flexibility for new designs in PC and Network products; in addition,

to participating into consumer electronic products," said Max Bathaee, Sr. Marketing Manager for Network Storage Products at Atmel.

AT78C5081 is available in TQFP 100-pin package. Pricing is based on volume shipment or \$1.95 for 10K and below volume. AT78C5090 is available in QFP 120 pin package. Pricing is based on volume shipment or \$2.95 for 10K and below volume. Both products are available in a variety of packages based on customer requirements.

## IPWireless and Atmel Partner to Develop UMTS TDD/VoIP Mobile Handsets

Atmel and IPWireless announced that they have collaborated, along with an OEM, to develop a UMTS TDD mobile handset. The mobile handset will allow UMTS TDD network operators to offer carrier-grade mobile voice over IP (VoIP) services, in addition to existing broadband and other packet based services, on their converged networks. IPWireless and Atmel have already completed the first successful transmission of a call from a mobile VoIP handset over UMTS TDD, an important milestone in the development of commercial UMTS TDD handsets.

UMTS TDD, the 3GPP standard optimized for highspeed data, is ideal for carrier-grade voice applications with its high capacity, low latency, and low power requirements. IPWireless' latest UMTS TDD software supports both dedicated and shared channels, enabling operators to deliver circuit-switched quality while enjoying packet-based system economic benefits. Operators can leverage existing network infrastructure to add VoIP over UMTS TDD services in a highly efficient, reliable, and economic manner, thereby increasing revenue while augmenting subscriber services. With a UMTS TDD VoIP handset, subscribers will experience the same quality of voice service they expect from traditional mobile phones. In addition, the handset's USB port allows users to connect it to computers or other devices and use it as a very high-speed broadband modem.

The UMTS TDD VoIP handset will use Atmel's highly integrated AT76C902 VoIP system-on-a-chip as the main processor, with the IPWireless TDD Module performing the UMTS TDD modem functions. UMTS TDD handsets prototypes will be ready by the end of 2004 with commercial availability of phones expected mid-2005.

## Web Site Expanded to Support Chinese Language

The Atmel web site, www.atmel.com now supports a Chinese language version. Users can now switch from

English to Chinese from any page of the site and smoothly navigate the site in the selected language. Specific information is available in simplified Chinese to introduce the company activity and the various Atmel product lines. Additionally, the majority of AVR® microcontroller datasheets have been translated in Chinese as well as other AVR related technical documentation. Atmel plans to progressively extend translation to other Atmel product literature to support the engineering community in mainland China and Taiwan.

According to Jensan Jen, Sr. Vice President and General Manager, Asia and Japan Operations, "Atmel

is a global player in the semiconductor market and our products are very well received in Asia. They are also among one of the favorites in the Chinese engineering community. Although many engineers have the professional level of English reading capability, it is still preferred to see Chinese website content and other technical documentation being translated, in order to easily comprehend and enhance the development efficiency."

We believe that this new web service combined with an increasing support from local technical teams, will significantly strengthen Atmel's presence in China," he added.

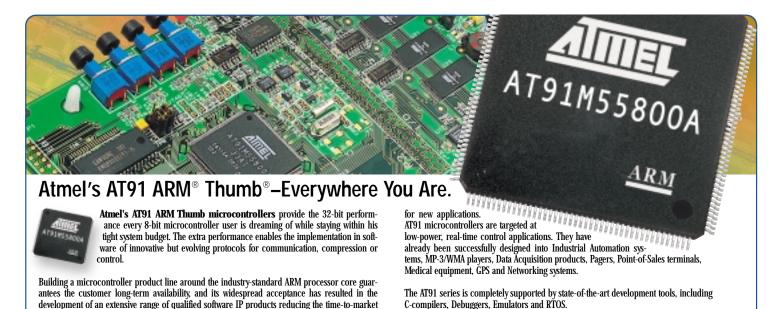

## First ARM7® Core-based Flash µC Under \$3 Introduced at ARM Developers' Conference

At the ARM Developers' Conference in Santa Clara last month, Atmel introduced the world's first family of ARM7 core-based flash microcontrollers with prices starting at less than \$3. The product line is targeted at 8-bit applications such as designs with in-system programmable Flash, single supply operation, BOD, POR, RC Oscillator, HW security and USB device.

The AT91SAM7S32 and the AT91SAM7S64 are the first members of a series of Small pincount Smart

ARM7 Microcontrollers (SAM7S-series) with Flash densities of respectively 32-kByte and 64-kBytes. A 128-kbyte and 256-kbyte version, the AT91SAM7S128 and AT91SAM7S256, are planned for availability at the end of this year. Besides a jump in real-time performance over 8-bit microcontrollers, they are the world's first 32-bit microcontrollers to integrate a complete set of secure operation functions including a watchdog clocked by an on-chip RC oscillator, power supply monitors and hardware protection of the Flash memory.

The AT91SAM7 microcontrollers are supported by low-cost development tools, bringing 32-bit real-time processing power to a wide range of cost-sensitive applications that have until now been limited to 8-bit performance. Target applications for the AT91SAM7S series include appliance control, utility metering, security systems, data loggers, USB-based mobile phone and PC accessories.

### **Ultra Low Power MP3 Decoder for Cell Phones**

The AT89C51SND2C is a new MP3 decoder which combines in a single package all features needed in a cell phone to play MP3 ring tones and to convert a cell phone into a pen drive. Integrated in a cell phone, the AT89C51SND2C can easily replace sound generators, while offering MMC/SD card reader capability, MP3 music decoding and USB connection to PC. This provides cell phone manufacturers with more functionality while reducing the system size and costs.

Derived from the AT89C51SND1C, a fully integrated standalone hardwired MPEGI/II Layer-3 decoder, with an 8-bit microcontroller core, handling dataflow and MP3-player control, the AT89C51SND2C offers 64 Kbytes of Flash memory, an embedded MP3 decoder, host communication (serial, parallel, USB) and a Multi Media Card interface. It also includes a high quality stereo DAC with a 50 mW earphone power amplifier, and a 500 mW speaker power amplifier.

The AT89C51SND2C has versatile functionality apart from generating MP3 tones. It can play MP3 music from the cell phone Flash through UART or SPI or from

the Flash card (DataFlash\*, NAND Flash, MultiMediaCard, Xd-Picture Card, Secure Digital, CompactFlash). It can also upload/download files into the cell phone NAND Flash or NOR Flash, upload files from the MMC to the cell phone NAND or NOR Flash.

"For just one dollar more, the AT89C51SND2C allows the cell phone manufacturers to get rid

of the MIDI sound generator while offering to the market a product with extended functionality," said Bernard Bancelin, Marketing Manager of Audio Line at Atmel. "With its compact package, and low power consumption down to 35 mA while playing music at 2.7 V, the AT89C51SND2C offers longer battery life with optimized space," he added.

The AT89C51SND2C is available in a BGA100 (9 x 9 mm) package for industrial temperatures. Pricing for

500,000-unit quantity per year is \$6.00. A masked ROM version is available for low cost application at \$4.50 for 500,000 units.

A complete development package is available to help designers develop their new applications. It includes an emulator, a development board (AT89DVK-04) and a remote MP3-reference design (AT89RFD-08). All boards come with complete MP3-player firmware, schematics and host drivers.

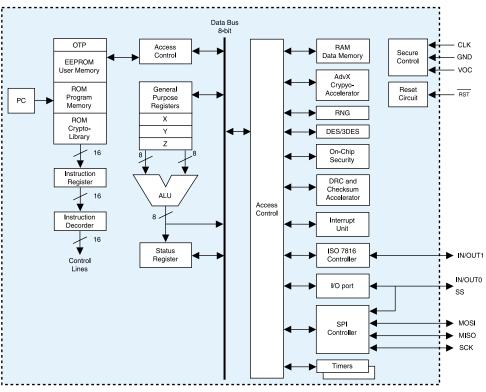

## AT90SC320288RCT High Security, High Performance, Cost Effective Member of the AT90SC Family

Atmel® Corporation introduces the AT90SC320288 RCT, a new member of the AT90SC family featuring outstanding on-chip compact memories: flexible 288-kbyte EEPROM, 320-kbytes of user-ROM, and 8-kbytes of RAM.

an existing product portfolio and offer new products with value-added services, quickly onto the market.

The AT90SC320288RCT can also be delivered with Atmel basic OS. When this basic OS is combined with

With this configuration, developers can create and test products with high flexibility and introduce products within extremely short time frames.

Targeting high—security markets, the AT90SC 32088RCT is designed to meet Common Criteria EAL5+ and Visa Level3 requirements. Like most of AT90SC SecureAVR products, this device features (but not only) true random number generator, DES/3DES hardware, unique chip ID, memories encryption, Memory Protection Unit, active shield protection, countermeasures against SPA, DPA, glitches and side channel attacks, as well as voltage, frequency, temperature and light protections...

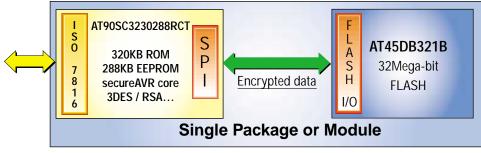

This device also features a SPI interface (up to 12 Mhz). The SPI interface can either be used as additional port to communicate with external device, or to connect an external Flash memory to create a very high secure mass storage device (see figure 2). In that case, data is ciphered by the high security and tamper resistant secure microcontroller (storing encryption keys) and transferred crypted to the Flash memory through the SPI interface.

On the top of the high speed high security DES/3DES engine, the AdvX® high performance cryptographic accelerator and it's embedded firmware (located in an additional 32KBytes dedicated-ROM) supports standard finite fields arithmetic functions including RSA, DSA, DH, ECC, AES.

Atmel hardware emulator "Voyager Emulation Platform "(ATV4) can be combined either with Software Development IAR Systems C-Spy Debugger or Atmel's AVR Studio Version 4.07. Software Libraries (crypto Hardware Abstraction Layers) and application notes are also available. The addition of accurate and complete documentation create a powerful user friendly development environment.

For more information on the secureAVR(tm) product family, please visit Atmel's website at: http://www.atmel.com/products/SecureAVR

Figure 1: AT90SC320288RCT block diagram

Thanks to the performance and the density of the 8-/16-bit RISC SecureAVR™ CPU architecture, Atmel can propose an attractive product for high density cost sensitive applications such as SIM/USIM cards. Combining advanced technologies and optimized architecture, the AT90SC320288RCT can run at high speed and be compliant with the most stringent industry standards such as mobile phone specifications.

The concept of product family allows developers to reuse existing OS/application software and get immediate access to a product featuring 288-kbytes of EEP-ROM memory with minimum effort. For example, a developer who has an operating system up and running on 32/36-kbyte of EEPROM (such as the AT90SC19236R/T) or 64/72-kbyte (AT90SC25672 R/T or AT90SC7272C) Atmel platform, can port it, with a very limited amount of resources and effort, on this new product and get access to a 256/288-kbyte EEP-ROM product. We believe that this will create unique opportunities, for mobile network operators, to extend

the memory management block. It allows program developers to use the 288-kbytes of non volatile memory either as program memory or user memory.

For examples this device can be used as a 144-kbyts Program (Flash functionality) + 144-kbyte EEPROM or 160-kbyte of program and 128-kbyte of EEPROM, or 224-kbyte program and 64-kbytes EEPROM,...

Figure 2: SIP Interface

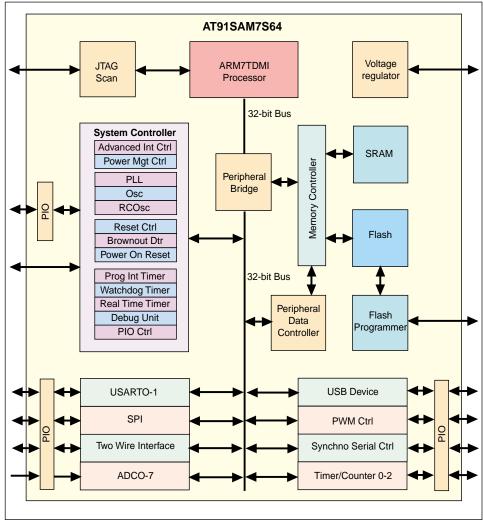

ATMEL® 'S AT91SAM7S SERIES OF ARM® -BASED FLASH MICROCONTROLLERS AIM TO BRIDGE THE GAP BETWEEN 8- AND 32-BIT MICROCONTROLLER APPLICATIONS. IN PARTICULAR THEY FOCUS ON REAL-TIME CONTROL APPLICATIONS THAT REQUIRE FEATURES TRADITIONALLY INCORPORATED INTO 8-BIT MCUS (NOTABLY A DETERMINISTIC RESPONSE TO COMMANDS AND INTERRUPTS) TOGETHER WITH THE SUPERIOR PROCESSING POWER AND EXTENDED ADDRESS SPACE OF 32-BIT MCUS. THIS ARTICLE REVIEWS THE GENERAL ARCHITECTURE OF THE AT91SAM7S SERIES AND GIVES DETAILS OF THE UNIQUE FEATURES THAT ATMEL HAS BUILT INTO THESE PRODUCTS IN ORDER TO ENSURE A DETERMINISTIC RESPONSE TO AN EXTERNAL EVENT: A GUARANTEED RESPONSE WITHIN A

SPECIFIED TIME INTERVAL.

## Atmel's ARM-based Flash µCs Optimized for Real-Time Control Applications

By: Peter Bishop, Communications Manager, Atmel Rousset

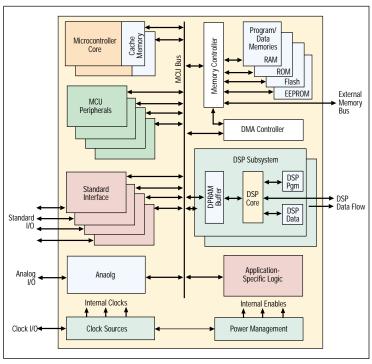

## AT91SAM7S Architecture and Real-Time Control Features

As shown in Figure 1, Atmel's AT91SAM7S series microcontrollers are built around a 32-bit ARM7TDMI® processor core and on-chip Flash and SRAM memories. Flash memory densities range from 32K to 512-kbytes. An integrated Flash Programmer facilitates programming (or re-programming) of the Flash memory as required. A memory lock bit, when set, makes it impossible to read the Flash memory by an external device, in order to protect valuable application code and sensitive data.

The System Controller includes a Brownout Detector and Power On Reset controller to ensure power-down

and power-up without accidental (or deliberate) corruption of data or code. A Voltage Regulator enables the device to be supplied by a single 3.3 V supply and a Power Management Controller can put the processor and any combination of peripherals into idle mode when they are not in use in order to minimize power consumption.

The rich peripheral set of the AT91SAM7S features a USB V2.0 full speed device for PC connectivity, and a number of peripherals adapted for real-time control. These include a Pulse Width Modulator, several Timers and Timer/Counters supported by on-chip Oscillators and a Phase Locked Loop, and an 8-channel 10-bit ADC. A Parallel I/O Controller multiplexes peripheral I/Os with a set of general-purpose I/O lines in order to reduce the pin count and provide flexibility of external access.

Figure 1: AT91SAM7S Architecture

## Single-Cycle Code Access from Flash Memory

The limiting deterministic performance of a fast processor running code from memory is established by the single-cycle access time of the memory. (Cache memories cannot be used where deterministic performance is mandatory.) Atmel's integrated high-speed Flash memory is capable of single-cycle access in 33 ns, giving maximum deterministic performance by the ARM7TDMI processor of 27 MIPS. This is a significant improvement over 8-bit MCU performance under deterministic conditions.

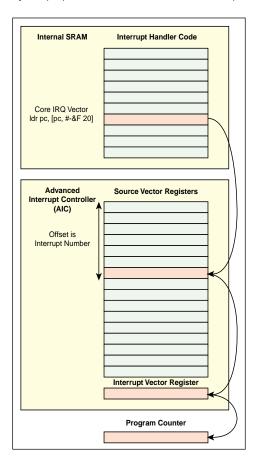

#### **Rapid Interrupt Handling**

Real-time control applications are typically interrupt-driven, with a response required within a specified time to each external event. Atmel has significantly enhanced the basic interrupt structure of the ARM7TDMI processor in order to provide an interrupt handling capability that meets this requirement. The Advanced Interrupt Controller (AIC) controls the two interrupt lines of the ARM7 processor (normal and fast interrupt). It provides a set of individually maskable, vectored interrupt sources with 8-level priority. One source is for the fast interrupt request, one is for the system peripherals and the remainder are for interrupts

Figure 2: AT91SAM7S Advanced Interrupt Controller

from peripherals or external sources. The basic interrupt handler, permanently stored in SRAM, resolves interrupt priorities and then executes an instruction that uses the interrupt number as an offset to load the vector for the required interrupt service routine directly into the Program Counter (Figure 2). This simple, robust mechanism ensures the transfer of control to the required interrupt service routine in the minimum number of instruction cycles.

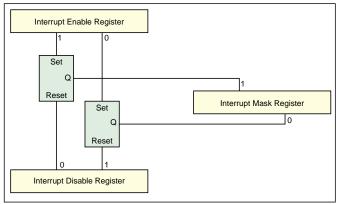

#### **Single-Cycle Bit Set and Reset**

Control applications frequently require individual bit set/reset operations, but the basic ARM7 processor architecture requires that this be accomplished by a read-modify-write sequence of operations that requires interrupt masking (itself a bit set/reset operation) to ensure that the entire sequence is carried to completion once it has started. To overcome this shortcoming, Atmel has provided the AT91SAM7S series with an atomic bit set/reset facility that works in the same way for all the peripheral control/monitoring registers.

As shown in Figure 3, complementary Enable and Disable Registers are connected by RS flip-flops to each Status Register. A bit is set in the Status Register by writing 1 to the corresponding bit position in its Enable Register (writing a zero has no effect). Writing a 1 in the Reset register clears the corresponding bit in the Status Register.

Figure 3: AT91SAM7S Register Bit Set/Reset Mechanism

This provision, commonly found in 8-bit microcontrollers, reduces bit manipulation to a single instruction executed in a single clock cycle. It reduces code size (by approximately 60% for the instruction sequence concerned) and speeds program execution.

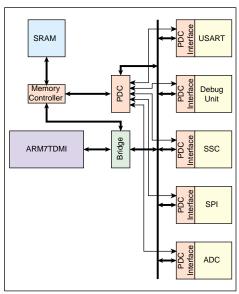

## Peripheral Data Controller for Direct Memory Access

Many of the AT91SAM7S peripherals are designed to transfer blocks of data between SRAM and an external communications channel (USART, Debug Unit, SSC, SPI and ADC). In order to carry out these transfers as efficiently as possible, Atmel has incorporated a Peripheral

Figure 4: AT91SAM7S Peripheral Data Controller

Data Controller (PDC) into the AT91SAM7S architecture that provides a direct memory access (DMA) function.

The PDC (Figure 4) manages the transfer of blocks of data between SRAM and these serial peripherals with minimum processor overhead. On the one hand this reduces the programming requirement for data trans-

fers to writing or updating the contents of the appropriate PDC Interface registers, and on the other hand the transfer time for blocks of data is considerably reduced. The transfer of successive blocks can be chained to avoid generating unnecessary interrupts until the entire transfer is complete. These features significantly enhance the real-time performance of the AT91SAM7S.

#### Conclusion

The AT91SAM7S series incorporates a number of architectural features that bring the real-time

control capabilities of 8-bit microcontrollers into the 32-bit arena with hardly any price adder. Most of these features are Atmel enhancements to the basic ARM7TDMI architecture, with the common aim of providing deterministic performance at a clock speed and data throughput significantly higher than can be achieved with 8-bit microcontrollers. At the same time these devices achieve a commendably low power consumption while driven from a single-voltage supply, and protect valuable application code and reference data.

Further information can be obtained from Atmel's Web site at <a href="https://www.atmel.com">www.atmel.com</a>.

THIS PAPER PRESENTS A UNIVERSAL

RECONFIGURABLE SOPC PLATFORM

BASED ON A COMBINATION OF THE

ATMEL AT94K FPSLIC DEVICE AND AN

EXTERNAL MEMORY. THE PRESENTED

PLATFORM INCREASES THE POWER OF

THE FPSLIC DEVICE BOTH BY EXTENDING

THE INTERNAL ADDRESS SPACE THROUGH

AN INTRODUCTION OF A VIRTUAL PROGRAM MEMORY AND BY PROVIDING A

TRANSPARENT INFRASTRUCTURE FOR

FPGA RECONFIGURATION. THE PLATFORM

IS DEMONSTRATED ON TWO SIMPLE

DESIGNS THAT DEMONSTRATE BOTH

ASPECTS.

## Reconfigurable System on a Programmable Chip Platform

By: M. Danek, P. Honzık, J. Kadlec, R. Matousek, Z. Pohl of the Institute of Information Theory and Automation, Dept. of Computer Science & Eng. and Centre of Applied Cybernetics\*

#### Introduction

Field-programmable gate arrays are configurable VLSI devices that can implement various logic functions. Classical SRAM-based FPGA chips introduced in 1984 were designed to be configured only once at the beginning of their operation and to enable a designer to improve the functionality after a device was shipped to the end user.

Now, almost two decades later, the current FPGA technology includes the concept of reconfigurability. The reconfigurability has to be looked at from two levels. One level is the actual dynamic reconfigurability of a device, while the other is a support built into the CAD tools supplied for the device. At present, devices that support limited or full version of limited reconfigurability are available, for example, the recently introduced devices from Xilinx (Spartan2, VirtexII) or Atmel (AT40K, AT94K), but it has not been incorporated into the supplied design tools [3]. The reason for the latter fact is the rather complicated methodology that has to be implemented in the tools [6].

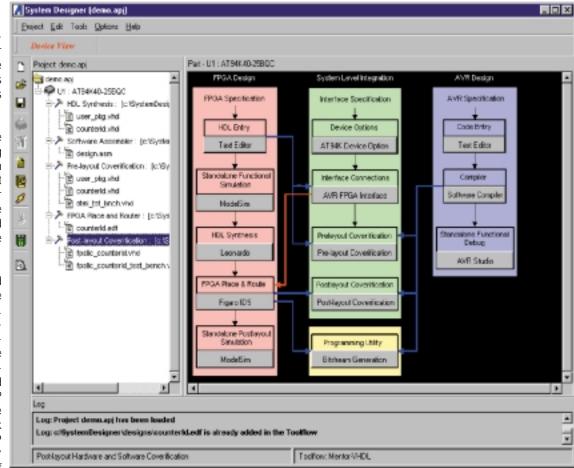

This paper describes a universal reconfigurable SOPC platform built around the Atmel AT94K FPSLIC1 device. The platform enables a software programmer to take advantage of a possible hardware implementation of a user function while not being directly involved in the hardware design process. This is made possible by providing a universal transparent hardware-software interface and a library of pre-compiled configuration bitstreams that are selected by the programmer according to the required hardware functions.

The platform implements an extended virtual memory space that increases the standard 64KB address space that is accessible by the FPGA and AVR processor inside AT94K. The extended memory space can be used for AVR programs, data, and FPGA configuration bitstreams, which increases the power of the AT94K device [5]. Similar architectures can be found in [1], [2].

The paper is structured in the following way: Section 2 describes basic features of the AT94K device, Section 3 presents basic features of the presented platform, Section 4 shows the use of the platform on two sample applications, and Section 5 concludes the paper.

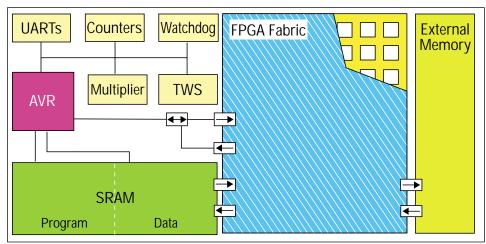

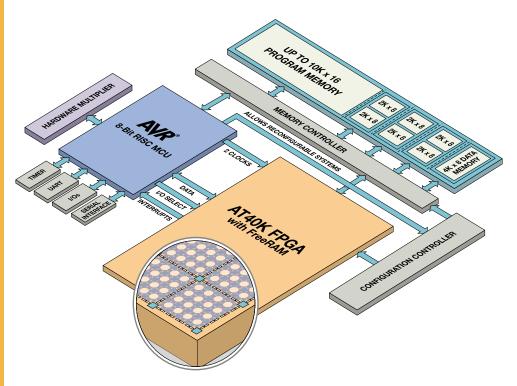

#### **AT94K FPSLIC**

The Atmel AT94K device (see [11] and Figure 1) consists of an AT40K FPGA [12], an 8-bit AVR microcontroller, a hardware multiplier, two UARTs, a two-wire serial port (TWS), three counters, a watchdog timer, and a 36KB SRAM memory that is partitioned to a 20-32KB AVR program space and a 4-16KB AVR data space. Prototyping boards based on this device are available from Atmel (ATSTK94, ATSTK594).

The AVR microcontroller can be programmed both in assembler or in C compiled, for example, by the Imagecraft C compiler or the free AVR gcc compiler.

The FPGA can be programmed by bitstreams generated by the Atmel-supplied Figaro place & route tool in combination with common design synthesis tools (Mentor Graphics Leonardo Spectrum, Synplicity Synplify, etc.) [8], [9].

The AT94K device can implement both pure AVR or pure AT40K designs or their combination. The standard AVR-FPGA data interface consists of 8 data inputs, 8

Figure 1: AT94K with an external memory. Arrows denote the direction of the data ports.

<sup>1</sup>Field-Programmable System Level Integrated Circuit

<sup>\*</sup> This work has been partially supported by the EU IST programme under No. IST-2001-34016 and by the Grant Agency of the Czech Republic under No. 102/04/2137.

#### Microprocessors In-Depth

data outputs, 16 FPGA select lines generated by the AVR, and 16 AVR interrupt lines generated by the FPGA. The FPGA can access both the AVR program area and AVR data area of the built-in SRAM. In addition, the AVR can reconfigure the FPGA using Mode 4 bitstreams and four FPGA configuration registers (FPGAX, FPGAY, FPGAZ, FPGAD) [10], [11].

AT94K alone is suitable for simple tasks that do not deal with large amount of data and that do not require high data throughput. Fortunately the AT94K target is supported by available C compilers, so programming the AT94K is a matter of routine C programming and FPGA design.

Its limits are mainly the size of its internal memory and the rather small size of the built-in AT40K FPGA. The internal memory is 36KB, out of which max. 32KB is available for program code and max. 16KB for user data. In the best configuration the built-in FPGA contains 50K equivalent gates. Also, the available C compilers do not provide any sophisticated interface to access the FPGA fabric.

#### **Extending the AT94K Power**

To increase the capabilities of AT94K it is necessary to increase mainly the real size of the program memory by implementing a virtual memory and the size of the data memory that stores FPGA bitstreams. Notice that a common size of a simple compiled AVR code is about 10KB; a common size of a moderate size bitstream in Mode 4 [10] is well over 100KB.

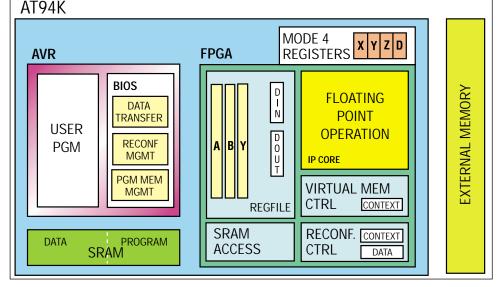

Both problems can be solved by using an external data memory. The proposed platform (Figure 2) uses an external FLASH memory to store fixed program and bitstream data that are copied at different times to specific locations of the internal SRAM memory. The FPGA is divided to a static part that implements an access to the FPGA reconfiguration data and the AVR program code, and to a dynamic part that contains user-defined designs; the designs can be reconfigured at run time.

#### Data Sharing between AVR and FPGA

Before the AT94K FPGA can be used as an AVR coprocessor, it is necessary to define data exchange schemes between AVR and FPGA. There are two possible schemes: to use registers implemented in the FPGA, or to use the internal SRAM.

The width of the FPGA registers is limited by the 8-bit AVR-FPGA data bus. The advantage of this scheme is its simplicity, a major drawback is its slow transfer rate: each AVR load or store instruction requires 2 clock cycles.

The SRAM exchange scheme is faster, since the FPGA can implement a DMA controller that can access the memory directly without an AVR support in one clock

cycle, which saves at least 4 clock cycles per operation (when processing one 8-bit data value at a time). Its disadvantage is the necessity to implement a data sharing or protection mechanism; in its simplest form it may be represented by a convention that a given memory area must not be modified by the AVR until the FPGA has finished the calculation.

#### **Virtual Program Memory**

The virtual program memory is often implemented using program overlays or memory paging. Since AVR is intended for simple tasks, we think that program overlays without memory protection are sucient. The following text considers 2KB long overlays, since this size seems adequate for AVR application programs. The data memory can be extended using a similar concept.

The implementation uses the fact that the program memory can be accessed as data by the FPGA by setting bit 36 in the FPSLIC system control register [11]. The implementation consists of two parts: a software overlay support contained in the AVR BIOS, and a hardware DMA controller implemented in the FPGA that transfers overlays from an external memory to a given location in the program SRAM. The DMA controller consists of a context register that determines the starting address (its MSbits) of the overlay in the external memory and of a 12-bit counter that generates the LS address bits of the overlay address. A write to the context register initiates a data transfer. When the counter overflows, it means that the transfer has been completed and the controller generates an interrupt.

Since a sequence of locations as accessed by the AVR in the program memory maps to diferent clusters of locations in the data memory, it is necessary to translate the compiled overlay code. It is convenient to perform this translation at compile time, since the resulting data can be just streamed from the external memory to the internal SRAM memory by the DMA controller each time an overlay is required and no run-time address translation is necessary.

The overlay service is accessed through a BIOS function call with a parameter that identifies the required overlay. This parameter is translated and stored to the context register. The BIOS function ensures that on completion the memory contains a valid overlay, a jump to its starting address is then performed in the application program.

#### **Programming Overlays in GCC**

The overlay concept requires that a common C program is transformed to several functions with a common start function, all contained in one overlay that is brought into the AVR program memory by the AVR BIOS on demand. The start function is similar to the main function in C. From the start function another sub-functions are called that are not visible from the AVR BIOS. The AVR BIOS can download a particular overlay to the memory,

and give control to the start function in the actual overlay. The function for changing overlays is a loop that checks the ID of the actual overlay in the memory and compares it with that of the required overlay. When a different overlay is requested, it must be downloaded from the external memory (in our case, an external flash memory is used to store overlays). The overlay transfer process is carried out by the FPGA logic; when a user program calls a particular overlay, the call initiates an FPGA-controlled DMA transfer. On completion the FPGA generates an interrupt.

The AVR BIOS does not write into the program space or call any function from the overlay memory. The AVR BIOS knows only the overlay starting address; an overlay is executed by a function call to that address. Each overlay needs to communicate with the AVR BIOS. To do this a service table is located at a fixed address in the AVR BIOS. The service table describes calling addresses of services that are provided by the AVR BIOS. The services include registering an interrupt, or starting a timer. This organization ensures the independence of overlays; the only implementation-dependent part of an overlay is a header file with the definition of the service table.

#### **FPGA Run-Time Reconfiguration**

Run-time reconfiguration enables the designer to increase the functional density of the FPGA coprocessor, in other words, to download functions to the FPGA as they are needed. AT94K supports four configuration modes, out of which the simplest reconfiguration mode is Mode 4 (simplest = principally does not require an external hardware). Mode 4 reconfiguration is based on four configuration registers serviced by the AVR [10], [11].

The most convenient implementation of the extended bitstream memory uses one FPGA register for context (bitstream) selection and another for data passing. The static part of the FPGA implements an address register that consists of the context register (MS bits) and a counter. On writing to the context register the counter is reset. Each time the data register is read by the AVR the counter increments. When the top address specified in the bitstream header is reached, i.e. when the reconfiguration of the dynamic part is finished, the FPGA interrupts the AVR operation.

When not considering different execution time due to reconfiguration, the reconfiguration process is transparent to the application software. The access to the FPGA coprocessor is implemented as a special BIOS function, whose parameters are the required operation and its operands passed either as direct values in the case of the register transfer, or as a starting address of their location and their number in the case of the SRAM transfer. When BIOS detects a request for an operation different than the one currently present in the FPGA, it calls a function that reconfigures the FPGA.

#### Migroprocessors In-Depth

This function first translates the requested operation to the context (address) of the corresponding bitstream and writes it to the context register. Then it sequentially reads 4-tuples of values and writes them to the four FPGA configuration registers (X, Y, Z, D) until the FPGA generates an interrupt.

#### **Generation of Reconfiguration Bitstreams**

The runtime reconfiguration of the AT94K FPGA fabric requires partial bitstreams. Such bitstreams reconfigure only a part of the chip while the rest is not a ected in its operation. The Figaro design implementation tool provided by Atmel is meant to generate bitstreams that are not intended for partial reconfiguration of the FPGA. A special implementation procedure must be used to obtain such bitstreams [3]. The idea is to get several complete bitstreams with all different coprocessor contexts that contain the same placement and routing of the identical static part.

The Figaro tool works with a system of libraries. Any design component can be implemented as a macro and stored in a named library. The top-level design may contain instances of such components as black boxes (i.e. without a description of their content). Figaro will then search project libraries for components that fit the instance interfaces.

This feature is used in the described approach to implement and store different contexts of the reconfigurable coprocessor in libraries with different names. Since all contexts are implemented, the top-level design can be opened in a new project that includes only one of the context libraries. A complete bitstream is generated by performing all implementation steps.

The next complete bitstream with a different coprocesor context must contain the same placement and routing of the identical static part. This is achieved by

opening the same project under a different name with the placement and routing locked. Before the project is re-opened, the context library must be changed to the next coprocesor context. The Figaro tool then detects that the coprocessor has changed and it reimplements only the coprocessor without any modifications in the locked static part. This procedure is repeated until all coprocessor contexts have been generated.

To obtain partial bitstreams the complete bitstreams obtained in the previous step must be compared using the Figaro bitstream compression tool. The tool generates incremental changes that must be performed to switch from the configuration given by the base bitstream to the configuration given by the new bitstream. To be able to use the partial bitstreams for changing the coprocessor configuration all possible coprocessor context swap combinations must be generated. A direct approach leads to n! combinations (each to each), where n is the number of contexts. A significant reduction of combinations is obtained by introducing a common reference coprocessor configuration, such as an empty contents or the most frequently used function; this approach decreases the number of necessary bitstreams to 2n.

#### **Sample Applications**

The described platform (Figure 2) is presented on two simple applications: the first shows the use of overlays, the second demonstrates a transparent run-time reconfiguration of the FPGA triggered by the application program.

#### **Program Overlays**

Program overlays are user-defined functions compiled as a standard C code with a specific starting address, here denoted as *START\_PROGRAM* (Figure 3). The overlays are implemented as data transfers from the external memory to specific locations in the program

memory. The START\_PROGRAM value has to be set in accordance with the starting location used by the FPGA DMA controller. Once the overlay has been loaded, the application code performs a jump to the START\_PROGRAM location (appl is a pointer to a function). When the overlay finishes, the control is returned to the main application, which can load and execute another overlay.

The *LoadOvly* function implemented in BIOS translates the overlay ID to its context in the external memory (its MS address bits) and stores it to the *VIRTUAL MEM CTRL* context register (Figure 2). This write initiates a DMA operation (implemented in the FPGA) that transfers a 2KB block of data from the external memory to the AVR program SRAM. Once the transfer is completed the FPGA generates an interrupt.

```

if (LoadOvly(ovlyID) != TRUE)

PrintStr("OVERLAY LOAD FAILED\r\n");

else {

appl = START_PROGRAM;

appl();

}

```

Figure 3: An overlay use in an application program.

```

len = LoadData(&oper,data);

i=0;

while (i<(len/6)) {

CallFPGA(oper,

data[6*i],data[6*i+1],data[6*i+2],

data[6*i+3],data[6*i+4],data[6*i+5],

&results[3*i], &results[3*i+1],

&results[3*i+2]);

i++;

}</pre>

```

Figure 4: An FPGA call in an application program.

#### Reconfigurable Coprocessor

The reconfigurable coprocessor implements different operations executed in the FPGA. The coprocessor can be accessed by an application program executed by the AVR microcontroller.

In the described application the coprocessor implements basic floating-point operations - ADD, MUL, DIV, SQRT - in a 24-bit precission (1-bit sign, 6-bit exponent, 17-bit mantissa). As the AT40K40 FPGA is too small to contain all the operations at once, the coprocessor is reconfigured prior to calculation when necessary.

The performed task is simple: the AVR gets a data block from the serial port, then it uses the FPGA floating-point coprocessor to calculate results for these values.

Figure 2: The AT94K-based reconfiguration platform.

#### Microprocessors In-Depth

The design consists of four main parts (Figure 2):

- 1. the floating-point coprocessor implemented in the FPGA, denoted as *IP CORE*.

- 2. the data management, i.e. the data transfer part of the AVR BIOS and the *REGFILE* and *SRAM ACCESS* blocks in the FPGA,

- 3. the virtual memory management, implemented in the *PGM MEM MGMT* part of the BIOS and the *VIRTU-AL MEM CTRL* block in the FPGA,

- 4. and the reconfiguration controller, shown in BIOS as *RECONF MGMT* and in the FPGA as *RECONF CTRL*.

A sample application program built upon the infrastructure is shown in Figure 4. The code first gets a data block, then it calls the FPGA to process the data. The first item in the block determines which operation should be performed, this is stored in the *oper* parameter.

The FPGA infrastructure is transparent to the programmer. The only place at which the AVR-FPGA interaction can be noticed is the function call CallFPGA. Each operand in the example is encoded using 24 bits; the amount of parameters passed to the function is determined by the 8-bit architecture of the internal AVR-FPGA data bus. An additional parameter called oper parameter is passed to the AVR BIOS to determine if it

is necessary to reconfigure the FPGA. The BIOS then transfers the data to the coprocessor and gets the

#### Conclusion

This paper has presented a hardware platform that makes use of dynamic reconfiguration to increase a computational potential of a simple microcontroller. The platform uses an external memory to emulate a bigger program and data space, and to store reconfiguration bitstreams needed to program an FPGA-based accelerator connected to the microcontroller. Two sample applications have demonstrated the transparency of this approach in terms of application programming.

The most important advantage of the presented approach is the possibility to offer an unlimited number of different operations accelerated in the FPGA to an application programmer without his concern for digital circuit design.

#### Acknowledgements

The authors would like to gratefully acknowledge the support for this work provided by Atmel Hellas and Atmel Nantes.

#### References

[1] Collahan, T. J., Hauser, J. R., Wawrzynek, J.: The Garp architecture and C compiler. In IEEE Computer, vol. 33, iss. 4, 2000, pp. 62–66.

[2] Horta, E. L., Lockwood, J. W., Taylor, D. E., Parlour, D.: Dynamic hardware plugins in an FPGA with partial run-time reconfiguration. In Proceedings of the Design Automation Conference, 2002, pp. 343–348.

[3] Matousek, R., Danek, M., Pohl, Z., Kadlec: Dynamic runtime partial reconfiguration in FPGA. In ECMS2003, Liberec, 2003. pp. 294–297.

[4] Matousek, R., Pohl, Z., Danek, M., Kadlec, J.: Dynamic reconfiguration of FPGAs. In 10th International Workshop on Systems, Signals and Image Processing (IWSSIP'03), 2003, pp. 288–291.

[5] Wirthlin, M. J., Hutchings, B. L.: Improving functional density using run-time circuit reconfiguration. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 6, Iss. 2, 2002, pp. 247–256.

[6] X. Zhang, Kam W. Ng: A review of high-level synthesis for dynamically reconfigurable FPGAs. In: Microprocessors and Microsystems, No. 24 (2000), pp. 199-211.

[7] FPSLIC User's Guide and Tutorials, Revision 5 (Compatible with SystemDesigner 2.1), shipped with the ATSTK94 starter kit. Atmel, 2001.

[8] FPSLIC System Designer 3.0 User Guide. Atmel, 2003.

[9] Atmel FPGA Integrated Development System. Atmel, 2001

[10] FPSLIC on-chip Partial Reconfiguration of the Embedded AT40K FPGA. Atmel, 2002.

[11] AT94K Series Field Programmable System Level Integrated Circuit. Atmel, 2002.

[12] AT40K 5K to 50K Gates Coprocessor FPGA with FreeRAM. Atmel, 2002

#### Integrated Development Tools for Embedded Microcontrollers

**Atmel:** T89C51RB2/RC2/RD2, T89C5111/5112/5115, T89C51AC2, T89C51CC01/02/03, TS8xC51U2, AT8xLV51/52/55, AT87F51/52/55, AT89C1051/2051/2051x2/4051, AT89C51/52/55/55WD, T89C51IB2/IC2, AT87F51RC, TS8xC51RA2, AT90S, ATtiny and others...

**Philips:** LPC760/761/762/764/767/768/769, LPC932/9xx, 80C31X2/51X2/52X2/54X2/58X2, 89C51RA2/RB2/RC2/RD2, 8xC660/662/664/668, P87C552/554, 87C652/654 and others...

Intel: 80C31/32/51/52, 87C51FA/FB/FC, 87C51RA/RB/RC, 8xC196KC/KD, 8xC196MC/MD/MH, 8xC196CB, 8xC196NT and others...

*Winbond:* W77C32/58; W77E58, W77L32, W77LE58, W78C54, W78C58, W78E516B, W78E51B, W78E52B/54/58, W78IE54, W78L51/52/54, W78LE51/52/54/58, W78LE516/532, W78LE52, W78LE54, W78C51D, others...

Dallas Semiconductor: DS87C310/320/520/530 and others...

SST: 89C59, 89F54, 89F58 and others...

*Microchip:* The entire PIC12, PIC16, PIC17, and PIC18 families including PIC16F627/628, PIC17C756, PIC16F877A, PIC16F818/819, PIC18F452, PIC18F458, PIC18F6620, PIC18F6720, PIC18F8620, PIC18F8720, PIC18F4320 and others...

Texas Instruments: The entire MSP430 family, TAS1020A, TUSB3220

Xemics: XE88LC01/05, XE88LC02, XE88LC06/06A

Sensory: RSC4xx

Hi-End Features @ Affordable Prices

ARM CORE ASIC PRODUCT

DEVELOPMENT IS POSSIBLE BY

THE MASSES, AND ARM CORE-BASED

STANDARD PRODUCTS OFFER PROVEN

PATHS TO ASIC SOLUTIONS.

RE-USABLE/RE-CONFIGURABLE ARM

PERIPHERAL IP IS A REALITY. ASIC

SYSTEM SOFTWARE TEAMS CAN

TAKE ADVANTAGE OF ARM STANDARD

PRODUCT SOFTWARE, AND ATMEL'S

SILICONCITY PLATFORM DESIGN

APPROACH ENABLES FIRST TIME

SUCCESS SILICON WITH REDUCED

DEVELOPMENT LEAD TIMES.

## Practical Aspects of ARM Core-based Product Development

## By: Jim Hallman, ASIC Design Manager, Atmel Corporation

ASIC development of embedded ARM microcontroller core systems often exceed engineering estimates and management expectations. One might conclude that only experts should attempt embedded ARM corebased ASIC designs. Solutions have evolved to reduce product development cycle time, cost and risk while avoiding unexpected pitfalls along the way. ARM corebased system-on-a-chip (SoC) products, should no longer be considered only by elite ASIC designers with lots of time and big budgets.

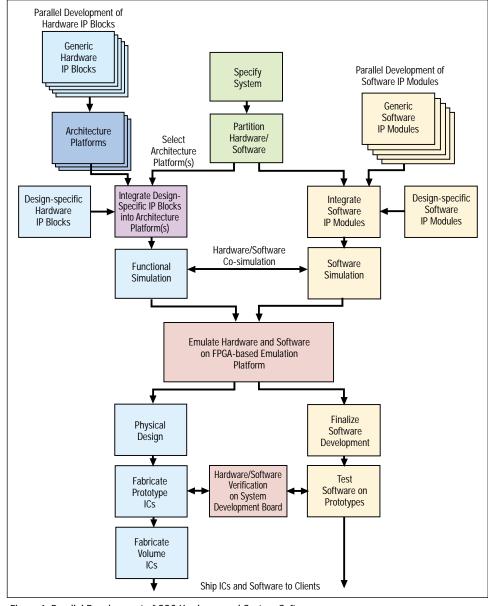

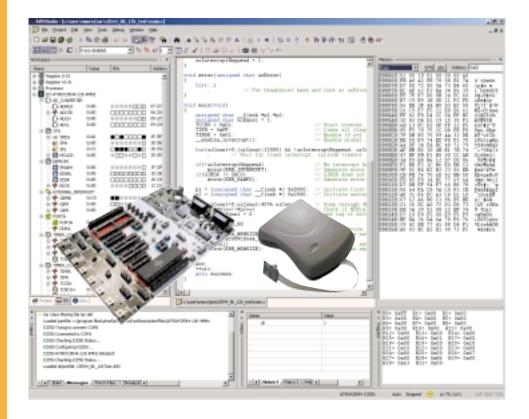

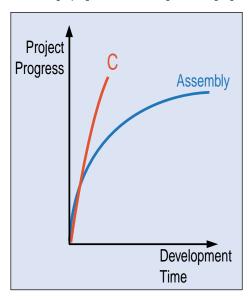

Bringing an ARM core-based SoC product to production involves more than the hardware implementation of an ASIC concept. Full system considerations, including software development, must be examined when a microcontroller is embedded inside the silicon. It is now practical to develop system software in parallel to SoC development (Figure 1), enabling product release to production soon after hardware silicon samples are reviewed.

Many ARM7 and ARM9 products have a common set of featured peripherals to complement the chosen core. General-purpose standard products address a wide

Figure 1: Parallel Development of SOC Hardware and System Software

#### Microprocessors In-Depth

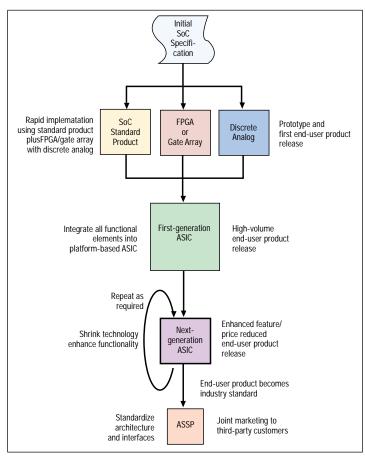

Figure 2: Product Evolution

application market, which means many features of the product go unused, even though paid for in silicon area. Systems typically want to use a large percentage of a selected standard product with the addition of application specific intellectual property (IP). This IP differentiates the end product from the competition. It is a natural progression for designers to begin a product development with a standard ARM product, complemented by an FPGA containing application specific IP or by discrete analog components. The product may even evolve into an application specific standard product (ASSP) marketed by the originator and the ASIC vendor (Figure 2). Atmel's approach to development, branded Silicon CITY™, encompasses standard product, ASIC and ASSP evolution into one common design and development environment. Atmel's SiliconCITY architecture platform and IP libraries permit migration of the utilized standard product components, application IP and analog into a single ASIC chip in a short period of time.

A key factor to reduce risk and design lead-time is to start development from validated and proven IP. Who wants to re-invent the wheel? SiliconCITY allows SOC designers to start ASIC product development from an SOC architecture platform netlist derived from a standard product netlist. Or they can start with a collection of IP building blocks used to create a standard product

Figure 3: SoC Architecture Platform

and configure their system netlist locally. Atmel introduces new ARM7 and ARM9 standard products through this same philosophy. An added advantage is

the portability of products across multiple ASIC technologies.

For an architecture platform design system (Figure 3) to be real, it must be flexible enough to address a wide range of user requirements. IP within the system must be configurable for multiple methods of use. However, flexibility introduces complexity from a synthesis and verification perspective. This can translate into time, diminishing the advantage of a platform-based design system. Highly parameterized IP is the answer. Atmel's IP has been designed not only for direct re-use, but also for expandability. Every component of the system uses parameterized IP in a common approach. A clearly defined data structure, common clock and test approach with global system constraint files, insure a consistent design methodology across selected IP. IP parameters extend into synthesis scripts and test benches to assure automated verification for each configuration.

Why emphasize IP parameterization? To dramatically reduce development lead times, IP must be configurable for use in multiple applications, while retaining a robust verification methodology. Parameterization allows bus interfaces and peripheral features to evolve with market needs. Bit-oriented peripherals can expand

or shrink to a specific configuration. Multiple functions can be duplicated. Standard interface protocols can be enforced or relaxed. System performance can demand increased pipelining of peripherals. A choice of multiple bus architecture interfaces expands usage options. System interfaces off-chip often have fixed requirements, which the ASIC must match. Designing IP to have a large feature set that can be selectively parsed down through parameters to meet multiple user needs, broadens the applications that may be addressed without excessive gate count overheads.

As an example of parameterization power, consider how the ARM AMBA bus standard has evolved. The APB protocol has changed between revision D (ASB) and revision 2 (AHB) related to the read data sampling and register reset timing points. An APB peripheral would require a different interface depending on the AMBA protocol in use for the overall system, requiring two versions of the peripheral design to be maintained.

However, all remaining features of the peripheral remain unchanged. Using a bus protocol parameter in the IP definition, "BRIDGE\_TYPE", as part of the RTL code allows the synthesis process to realize either protocol.

IP parameterization does not come without a price. Certainly parameterized IP requires longer up front development time by the provider, whether it is offered by an ASIC provider or an internal design team. A rigid data structure across all IP must be adhered to, while verification test benches and synthesis scripts tend to be more complex. With parameterization comes an

#### Microprocessors In-Depth

exponential increase in possible configurations, which leaves potential for verification holes in test benches for unexpected combinations. This also leads to heavier documentation to cover "what if" scenarios.

Is a strong link between standard product IP and ASIC design IP necessary? First time silicon success is critical in today's markets. By using identical IP blocks implemented in a standard product, the ASIC designer is comfortable knowing that many users have heavily exercised the block function, insuring robust logic. For IP blocks such as USB devices and multi-media card interfaces, software drivers from a standard product may be easily updated to operate with an ASIC. Even operating systems such as Linux® and Windows® can be quickly ported. A software development system from a standard product can be used to start ASIC code development while ASIC specific emulation systems are in development. If an ASIC product has evolved from a standard product implementation, the ASIC will be able to use a large portion of the software application code previously created by the product design team.

Serious developers of ARM core-based SoCs will include the creation of an ASIC specific product emulation board into the overall program development

schedule. Designers may create a specific board for their application or adopt a third party board, such as the Prototype and Emulation Platform (PEP) from Atmel, created for this purpose. This emulation board would include an ARM7 or ARM9 test chip, obtained from the ASIC manufacturer; an FPGA large enough to hold all of the ASIC logic, large memories; and numerous interface and clock circuits.

From a hardware perspective, the board will be used as an aid to prove hardware design of new system components. It can be used to heavily exercise components operating to a standard protocol. And it can be used to prove complex peripheral relationships not practical though ASIC simulation. From a software perspective, it provides the software team with a vehicle to exercise real application code. This will reduce software debug efforts when final silicon arrives. The software team may have started to prove their code using a code development board from an ARM standard product. They can now move this code over to the ASIC specific emulation system.

FPGA development should not be taken lightly. Too often ASIC design teams underestimate the effort required to configure an FPGA for an ASIC emulation system. This is often a project of its own requiring spe-

cific resources. ASIC designers must consider from the start that they will be partitioning the ASIC netlist for synthesis to an FPGA. Some logic does not lend itself to FPGA implementation and must be removed from the FPGA netlist. In other cases the ASIC design may be very large, exceeding the ability of a single FPGA. Third party tools can assist designers to prepare an ASIC netlist for FPGA porting. Preparing a solid hardware emulation platform in advance of the ASIC can have results that ASIC designers may not like. ASIC designers will spend time proving that "bugs" identified by the software team are in the software code and not in the hardware. This is an inevitable event that will occur at some stage of the product development, but it may also lead to discovery of true hardware "bugs". Addressing it early in the product development timeline increases the odds of first time success silicon but must be considered in the resource planning.

ARM core ASIC product development is possible by the masses, and ARM core-based standard products offer proven paths to ASIC solutions. Re-usable/re-configurable ARM peripheral IP is a reality. ASIC system software teams can take advantage of ARM standard product software, and Atmel's SiliconCITY platform design approach enables first time success silicon with reduced development lead times.

#### Start your journey today towards a successful design at: www.atmel.com/arm

| Eval Board | Microprocessor Supported                                           |

|------------|--------------------------------------------------------------------|

| AT91EB40   | Supports AT91X40, enabling code development & eval.                |

| AT91EB40A  | Supports AT91RO40008, enabling code development & eval.            |

| AT91EB42   | Supports AT91M42800A, enabling code development & eval.            |

| AT91EB55   | Supports AT91M55800A, enabling code development & eval.            |

| AT91EB63   | Supports AT91M63200 & AT91M43300 enabling code development & eval. |

2003 Atmel Corporation. Atmel and the Atmel logo are registered trademarks of Atmel Corporation

#### Memory Extension Card

#### AT91MEC01

Increases memory capacity of AT91 Eval. Board, adding 2M bytes of SRAM and 3M bytes of Flash on the external bus. Complete with application Guide.

Everywhere You Are™

## Designer's Corner

## Designing for Efficient Production with In-System Re-programmable Flash µCs

#### By: OJ Svendlsi

For products where time-to-market and efficient production is important, selecting the right microcontroller architecture plays a big role. To get the shortest possible development time, the following requirements should be filled:

· Good and easy to use development tools

- Enough resources on-chip to meet requirements

- Efficient for high level languages

- Flash program memory for fast and reliable programming

The megaAVR family from Atmel has all these features and more, making them a perfect choice for advanced products requiring short time-to-market.

This white paper discusses the advantages of this family related to getting the shortest time-to-market and the most efficient production once the product is ready.

#### **Development**

During development of a new product, the microcontroller is normally the most important module, and

always the component where the majority of the engineering hours are spent. Thus, making sure the microcontroller has what it takes to ease the development should be given some priority.

#### Selecting the Right Development Tools

When selecting a microcontroller, you are also selecting the development tools you are blessed with. These development tools range from the simplest evaluation kits to high-end In-circuit emulators and production programmers. Depending of the complexity of the end product, different debugging solutions will be optimal. A 1-2K microcontroller with a minimum of on-chip resources can often be debugged using a free architectural simulator such as AVR Studio. For complex applications on big parts with many peripherals, using an advanced In-circuit emulator with advanced features such as Trace capabilities, advanced breakpoints and Code coverage functionality might reduce the design time significantly.

Parts with on-chip debug capability offers a very low cost alternative for the debugging. The JTAGICE mk-II from Atmel is available for only \$299, but still provides debugging capabilities like breakpoints, data watch, single stepping through code and full overview of processor internal resources. An additional important

advantage of on-chip debug is that the debugging is done on actual production silicon. Because of this, many of the problems designers run into when switching from an emulator platform to the real thing is eliminated.

Starter kits are useful when evaluating a microcontroller that might fit in the application. Many starter kits can also be used as target hardware during initial code development before the target hardware is ready.

#### Programming in a High Level Language

By programming the microcontroller in a high-level language (HLL), like for instance 'C', it is possible to reduce the development time significantly compared to writing in assembly. Generally one can say that an experienced designer can write the same amount of lines of code per day in C and assembly. However, the code-lines written in C will do much more than the same number of lines written in assembly.

Typically, a program written in a high level language will also be much more structured than a similar program written in assembly. Because of this, it is generally easier to debug a program written in a high-level language.

Most 8-bit microcontroller architectures come with a C-compiler. However, there is a big difference in how efficient the architectures are for high-level languages, and how the C-code should be structured to be efficient with one particular microcontroller architecture. Generally one can say that accumulator-based architectures like the 8051 architecture from Intel works best with global variables, while register-based architectures like the AVR from Atmel works best with local variables.

The benefits of using local variables are that the code becomes more structured and the portability and maintenance of the code is simplified when compared to code written with very many global variables. It is also much easier to reuse code when it is written with extensive use of local variables. When all the parameters going in and out of a subroutine is defined in the function call, it is very easy to port that subroutine into a new project.

The biggest drawbacks of writing code in a HLL are that the code normally becomes bigger and slower than a similar program written in assembly. However, as the number of code-lines increases, the gap in size between the HLL code and the assembly code starts to shrink. For a typical AVR user, the crossover point where the HLL and assembly code is the same size is around 4K. However, the HLL code will almost never be faster than the assembly code. If execution speed of a certain part of the program is critical, the solution is often to write the code for the critical parts in assembly, and write the skeleton and less critical subroutines in HLL.

#### Integration

The level of integration in a microcontroller can also affect the development time, in addition to power consumption and board space. Integrated functions such as Brown-out protection, Watchdog timer and Power-on reset circuitry gives the most reliable operation of the microcontroller, while functions like integrated EEP-ROM, internal RC oscillator and strong push pull port drivers eliminates external components and reduces cost and complexity of the design. With fewer external devices on the PCB, the possibility of running into noise related problems is also reduced. Especially the internal RC simplifies the design from a noise tolerance point of view.

## In-System Programmable Flash Program memory

Having In-System reprogrammable flash memory simplifies the development of a microcontroller application significantly compared to ROM/OTP solutions. The devices can be soldered into the application, and then be reprogrammed when a problem with the code is found. Using the AVR microcontrollers, the reprogramming can be done either through the SPI interface, or if using a JTAG on-chip debug or programming tool, through the integrated JTAG interface. If using a boot loader with the self-programming memory, other communication channels can also be used to reprogram the devices. The non-volatile memories of the AVR devices can be used to store history when debugging a program. The contents of the memories can then be read out after the program is finished.

#### **Production**

The advantages of using modern flash microcontrollers do not stop when the development is completed. Also when in full volume production, the benefits are many as outlined here.

#### **Procurement**

When using Flash microcontrollers, it is much easier to handle the procurement of the products. It is often easier to handle surprise orders since the microcontroller used is a standard line item. The chance that other companies are using the same microcontroller is usually big. This makes it possible to stock the microcontroller both at the distribution level and at the device manufacturer. If the same microcontroller is used for a number of applications, inventory can be moved from one product over to another to maximize the revenue. Handling multiple versions

With a Flash microcontroller the same device can be used to handle multiple software versions. In many products, the only difference between a high-end and a low-end version of a product is the firmware. In these cases, a flash microcontroller is ideal. The PCB can be assembled and completely tested in advance. Once the order comes in for a specific product, the code for this product can be programmed in, and the product shipped to the customer.

Many larger manufacturers are selling the same product to different OEM customers. In many cases, the differences between the products shipped to these OEMs lies in the software. Again, an In-System reprogrammable flash microcontrollers can be programmed with the correct code at the production line. Alternatively, the OEM account can program the parts of the code that is individually changeable by using the boot-capability of the megaAVR devices.

#### Calibration

Many analog sensors have a relatively large offset error that needs to be calibrated out to achieve good measurements. Devices with integrated non-volatile data memory and high performance Analog to Digital converters are ideal for this. With the AVR microcontrollers, special calibration software can be used to run the calibration and store the calibration values in the internal EEPROM. After this, the main code can be programmed in, and use the values stored in the EEPROM.

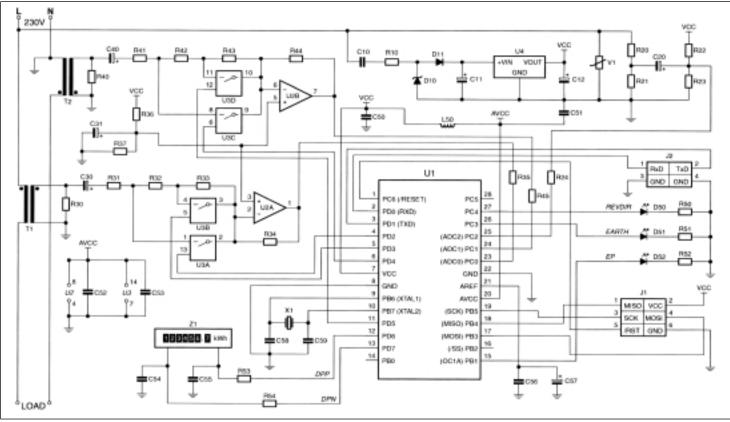

By: Flemming Christensen Managing Director, Sundance

Sundance's new high throughout configurable data acquisition module (DAQ), the SMT391, is the flagship of Sundance's new family of high performance data acquisition systems. The SMT391 is a powerful 1 giga sample per second (GSPS), dual channel analog-todigital converter (ADC). This high-performance 8-bit, DAQ system makes the SMT391 ideal for high bandwidth applications such as high-speed test and instrumentation, satellite communications, software defined radio (SDR), direct RF/IF processing, direct RF down conversion, and radar.

The SMT391, a "daughter module" that outputs data to a network of Sundance's reconfigurable computing and DSP systems, is managed by a Xilinx® Virtex-II Pro™ FPGA. The Virtex-II Pro FPGA, with its IBM PowerPC® embedded processor capabilities, manages the data transfers to a variety of communication channels such as ComPorts, Sundance High-speed Bus, and Xilinx RocketIO® Multi Gigabit Transceivers (MGTs). These channels are compatible to a wide range of Sundance processors and I/O modules. The FPGA controls all digital functions on the module as the digital output of the Atmel® broadband converter is fed into the FPGA. This data is then stored in an onboard DDR SDRAM for non real-time processing.

"The SMT391 leverages fully the power, performance and reconfigurability flexibility of the Xilinx® Virtex-II Pro™ and meets the stringent requirements of wireless and signal processing applications," said Dr. Nory Nakhaee CEO of Sundance. "The combination of Sundance's signal processing technologies and highspeed broadband expertise combined with the power of the Virtex-II Pro™, makes the SMT391 more than just a data acquisition module as it is also high-speed converter, a processor and a gateway to an array of powerful processing nodes," concluded Nakhaee.

A highly compact twin board design makes up the SMT391. A top layer board, the daughter board, is coupled to a base module via a Sundance LVDS Bus. This daughter board contains all the analog circuitry, the clock generation, trigger control, analog signal conditioning and as well a converter. This device handles all data acquisition and conversions. Analog data enters the top module via two analog data streams that are pre-conditioned before they enter the dual channel ADC converter. In conjunction to the two analog inputs, users can also provide the module with a custom clock and trigger. "Sundance was one of the first to recognize the benefits our Virtex-II Pro can offer to high speed broadband applications," said Jerry Banks, Director of Worldwide DSP Solutions Marketing at Xilinx. "The

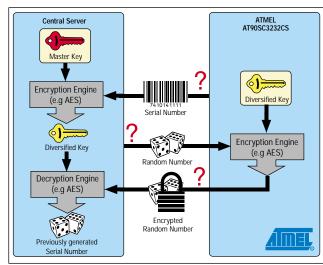

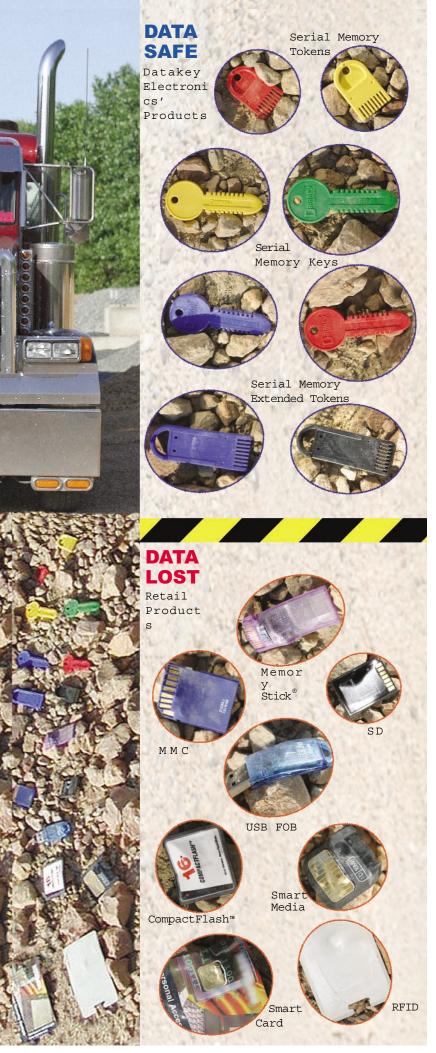

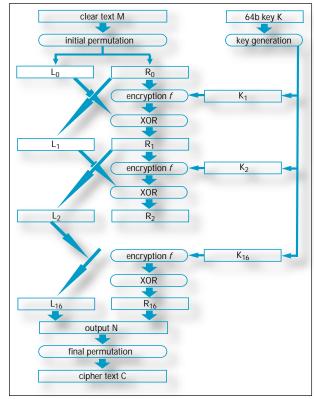

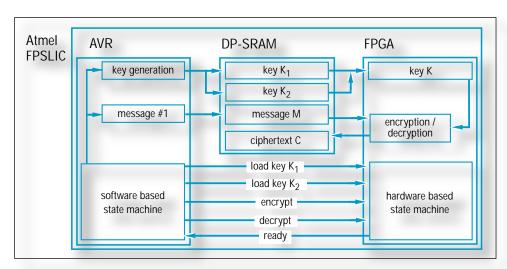

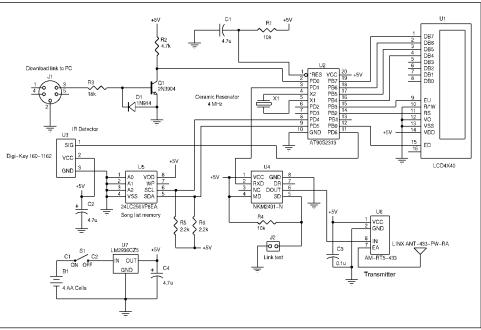

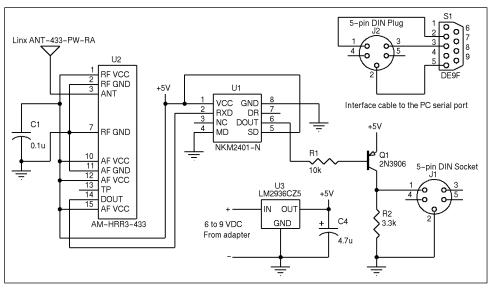

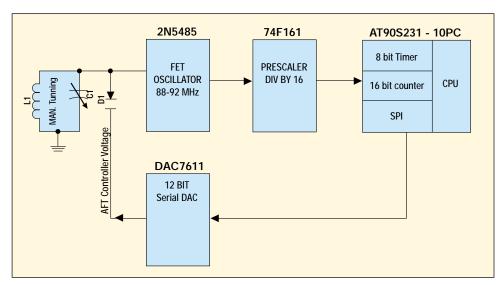

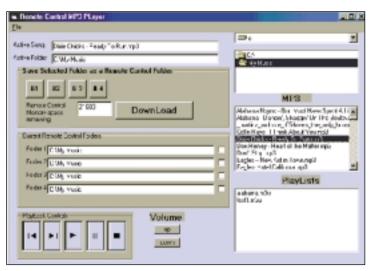

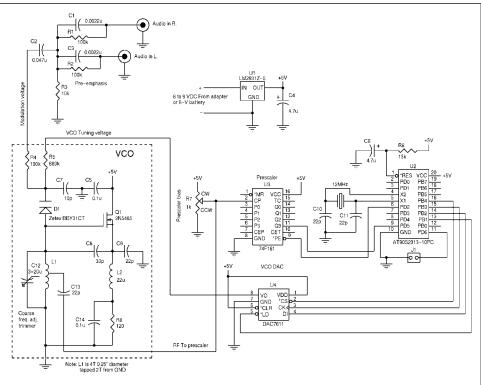

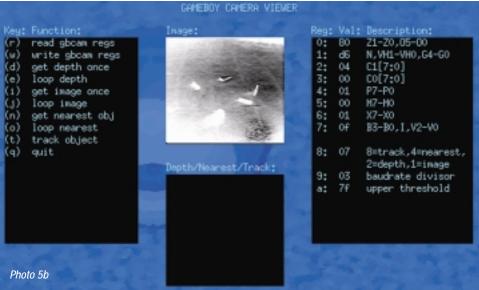

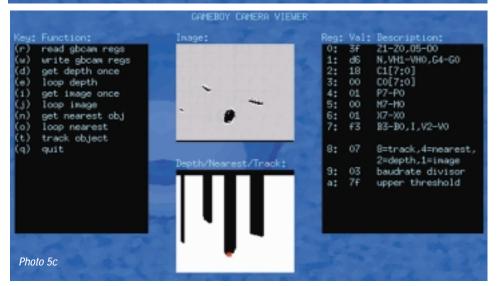

Sundance data acquisition system introduces a novel level of design, performance and flexibility that delivers the most advanced features engineers expect in a system oriented data acquisition module."